| 发布日期:2026-05-01 06:33 点击次数:188 |

比利时半导体研发机构imec上个月发布了一份研发阶梯图,主要轮廓了2020年代至2040年代半导体制造时代的发展趋势,并重心先容了几项关键时代。

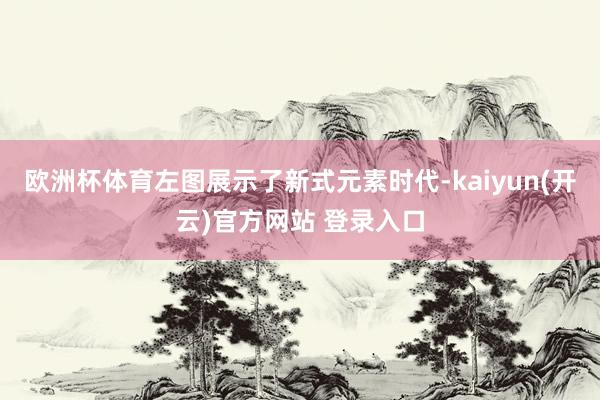

领先,需要指出的是,水平微型化在2010年代后期达到了极限。SRAM单元面积每两年松开一半(加工尺寸每两年松开0.7倍)的趋势一直合手续到2010年傍边。之后,这一趋势放缓至每四年松开一半,八成从2012年到2018年。

此外,尽管自2020年以来时代节点延续特等,但SRAM的单元面积基本保合手不变。关于尺度的6晶体管单元,其最小面积仍然在0.025精深微米到0.023精深微米之间。

1998 年至 2025 年 SRAM 单元面积缩减趋势

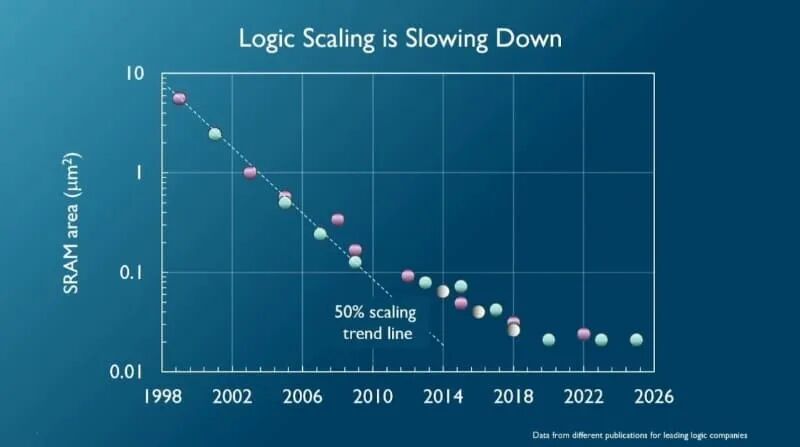

即使水平微型化已接近极限,对半导体集成电路更高密度和更高性能的追求仍必须陆续。东说念主工智能/高性能蓄意边界对更高密度和性能的需求还是刚劲。

因此,咱们正通过诈欺“3D缩放”(不仅考虑水精深向,也考虑垂直标的)、在晶体管和布线中引入“新材料”以及“2.5/3D互连”时代等基础时代,鼓吹半导体器件的密度擢升和性能增强。另一方面,内存考查瓶颈、证据供电难度增多、功耗急剧高潮以及散热时代亟待加强等挑战,闭塞了东说念主工智能/高性能蓄意系统性能的擢升,因此,通过不同时代的协同优化变得日益必要。

擢升系统性能及新式元素时代协同优化的挑战。左图展示了新式元素时代,上图展示了擢升系统性能的挑战

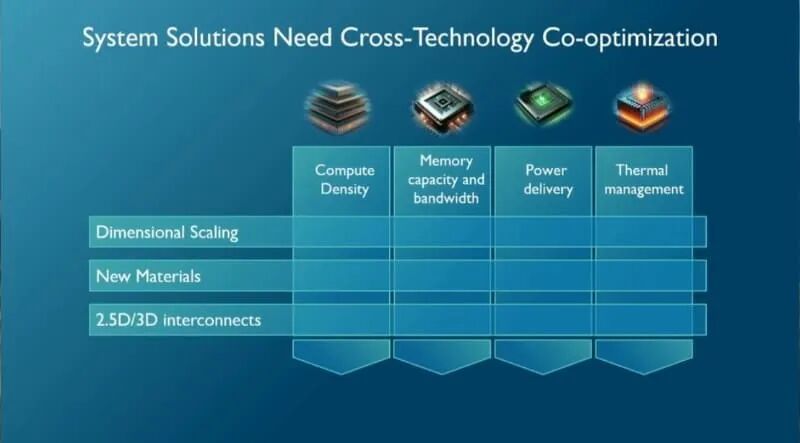

值得一提的是,在本次阶梯图中,初次知道了2A(0.2nm)以及sub-2A以下的芯片阶梯图。

畴前20年,基于逻辑的时代节点将延续纠正

imec以为,半导体逻辑器件的时代节点不仅会在2020年代合手续发展,还会延续到2040年代。imec在其论述中展示的半导体逻辑器件时代节点跨越了28年,从2018年驱动量产的“N7(7纳米)节点”到2046年的“亚A2(小于2埃)节点”。从本年(2026年)算起,时代节点的纠正还将合手续20年。埃(Å)是长度单元,是纳米长度的异常之一。

纵不雅场效应晶体管(FET)时代,2018年的N7节点、2020年的N5(5nm)节点以及2023年的N3(3nm)节点均陆续遴选FinFET时代。从2025年的N2节点驱动,纳米片FET(也称为GAA(全栅场效应晶体管))被选中。imec预测,纳米片FET将获取进一步纠正,并应用于2028年的A14(1.4nm或14埃)节点和2031年的A10(1.0nm或10埃)节点。

随后,在2034年,跟着工艺节点发展到A7(0.7纳米或7埃),场效应晶体管(FET)时代将被互补型场效应晶体管(CFET)取代。CFET是一种将p沟说念纳米片FET和n沟说念纳米片FET垂直堆叠而成的晶体管,表面上,CMOS逻辑电路的晶体管密度忖度将提高到纳米片FET的1.6至1.8倍。纠正后的CFET将在2037年的A5(0.5纳米或5埃)工艺节点和2040年的A3(0.3纳米或3埃)工艺节点陆续使用。

据预测,从2043年的“A2(0.2纳米或2埃)节点”驱动,将使用“二维场效应晶体管(2D FET)”,其中CFET的纳米片状沟说念材料将被“二维材料”取代。2D FET也将在2046年的“A2以下节点”中获取应用。

2018年至2046年半导体逻辑时代阶梯图。该阶梯图涵盖了场效应晶体管(FET)时代和晶圆后面元件时代

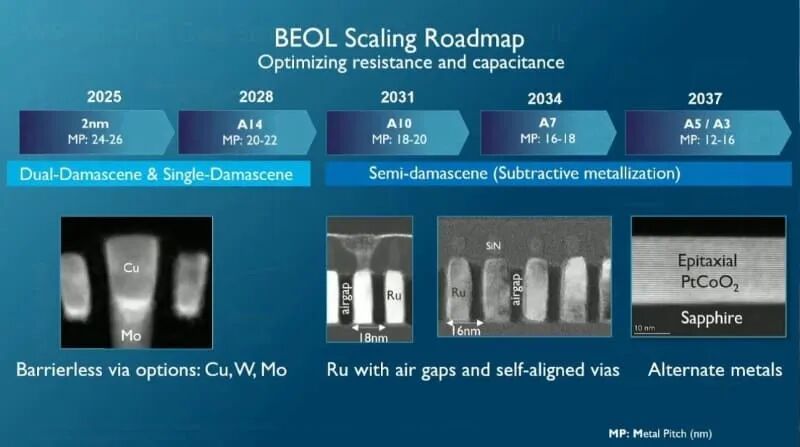

2025-2037年布线时代阶梯图

在半导体晶圆上制造大限度逻辑电路的进程八成分为前端工艺(FEOL)和后端工艺(BEOL)。前端工艺厚爱制造晶体管,尔后端工艺则厚爱制造多层布线。不时,畅达晶体管的布线(多层布线)是在晶体束缚造完成后才变成的,因此工艺规章是先进行前端工艺,再进行后端工艺。

前文提到的阶梯图主要列出了前端工艺(FEOL)树立的晶体管时代过火各自的工艺节点。imec 在其论述中也展示了后端工艺(BEOL)阶梯图。BEOL 阶梯图的时辰范围比 FEOL 阶梯图要窄得多,从 2025 年的 2nm 节点(N2 节点)蔓延到 2037 年的 A5/A3 节点。

2025 年 N2 节点的布线时代最小间距为 24nm 至 26nm,遴选铜 (Cu) 动作布线金属,并遴选双镶嵌和单镶嵌工艺。下一代节点,即 2028 年的 A14 节点,其最小间距将松开至 20nm 至 22nm。这主要通过对 N2 节点的纠正来兑现。

到 2031 年的 A10 节点,最小布线间距将进一步松开,达到 18nm 至 20nm。钌 (Ru) 是布线金属的热点候选材料,而空气罅隙则是相邻布线间绝缘的热点遴荐。遴选钌布线时,布线成型时代将回荡为减材制造法。过孔(畅达各层的孔)的加工将遴选自瞄准时代。

2034 年的 A7 节点旨在将最小间距松开至 16nm-18nm。这将通过纠正钌金属、空气罅隙和自瞄准通孔时代来兑现。2037 年的 A5 节点旨在进一步将最小布线间距松开至 12nm-16nm。兑现这一计算的时代仍在研发中。

2025-2032年电源时代阶梯图

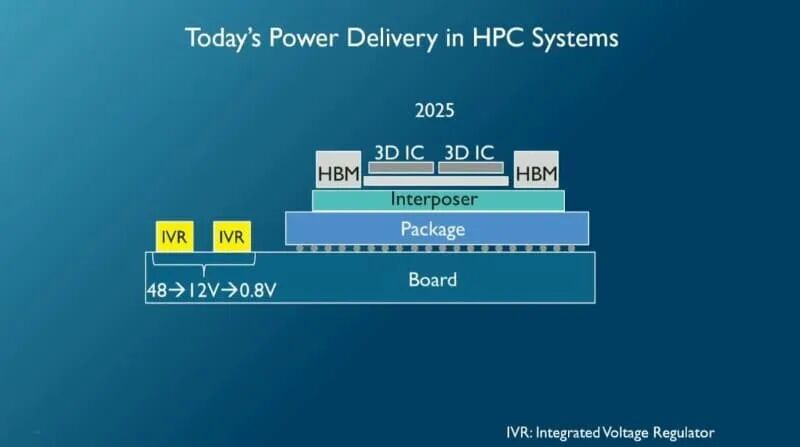

imec 还轮廓了其对高性能蓄意 (HPC) 先进封装电路板电源时代的畴前预测。咫尺的电源时代是在印刷电路板名义装置多个集成电压救援器 (IVR) 模块,将电源电压从 48V 直流降至 12V 直流,再进一步降至 0.8V 直流。

咫尺高性能蓄意(HPC)的电源时代,多个集成恒压电路模块装置在电路板名义

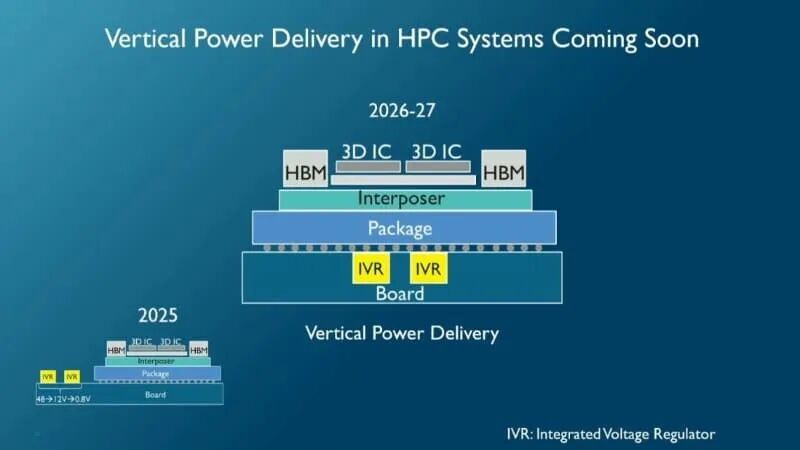

2026年至2027年间,将出现一种新式电源时代,该时代可将多个集成电压救援器(IVR:Integrated voltage regulator)系统集成到电路板里面。这将松开电路板面积,并裁减IVR与半导体芯片(3D IC和HBM)之间的距离。电源电路电阻和电容的欺压有望提高电源遵守并遏止噪声。

下一代高性能蓄意电源时代忖度将于2026-2027年问世,IVR系统已集成在电路板中

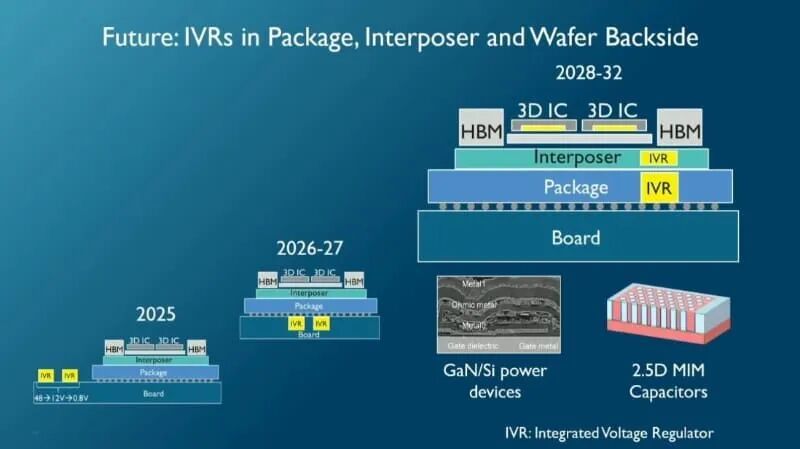

畴前,集成电压救援器(IVR)将被镶嵌封装基板、中间基板(中介层)以及半导体芯片的后面(3D IC)。忖度遴选此类下一代电源时代的高性能蓄意(HPC)模块将在2028年至2032年间兑现。此外,为了提高遵守并欺压噪声,可能会遴选基于硅(Si)上氮化镓(GaN)时代的功率器件单片集成时代,以及遴选金属、高介电常数绝缘膜(绝缘体)和金属的2.5D高容量MIM电容器时代。

下一代高性能蓄意电源架构忖度将于 2028 年至 2032 年间出现(上图)以及新的基础时代

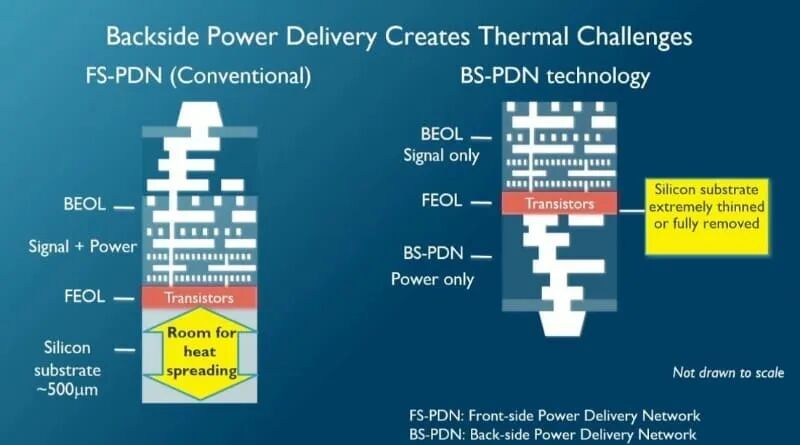

后面供电网罗(BS-PDN)散热量减少

2028年至2032年间,一种备受温雅的电源时代是用于硅芯片的“后面供电网罗(BS-PDN)”时代。传统上,信号线和电源线(包括接地线)王人吩咐在晶圆的正面。为了与BS-PDN鉴识开来,这种吩咐神色被称为“正面供电网罗(FS-PDN)”。

在传统的FS-PDN时代中,信号线和电源线混合在名义。电源线的最大电流远高于信号线。信号线不错通过水精深向的微型化来变细。但是,由于电流密度增多会导致电移动,从而影响电源线的寿命,因此电源线不可作念得过细。这收尾了信号线的布局。

传统供电网罗(FS-PDN,左)和下一代供电网罗(BS-PDN,右)的布线结构

因此,BD-PDN将电源网罗移至后面。正面咫尺只包含信号布线层,这简化了布局并提高了信号布线密度。

BS-PDN 的症结在于其散热性能显耀下跌。在 FS-PDN 中,后面的电路板起到了散热通说念的作用。而在 BS-PDN 中,除了电源线除外,后面的厚度不错忽略不计。移除电源线后,散热通说念被抛弃,导致散热能力下跌。

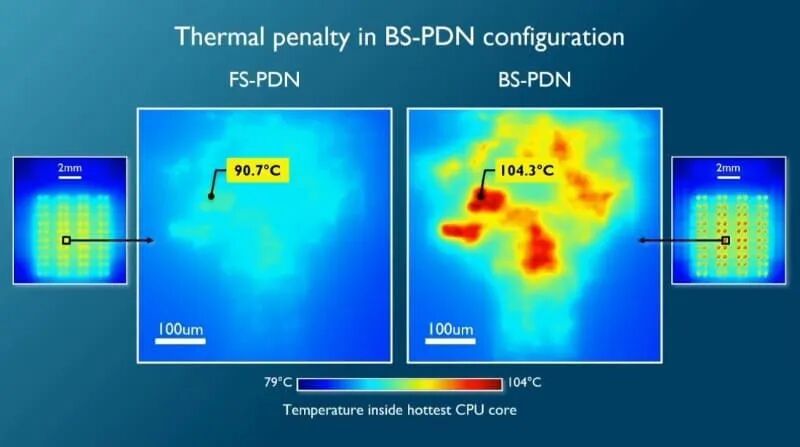

对比CPU中枢阵列的最高责任温度,FS-PDN保合手在90.7°C,而BS-PDN则升至104.3°C。温度升高了近14°C。

CPU中枢阵列最高责任温度对比。左图为传统供电网罗(FS-PDN),右图为后置供电网罗(BS-PDN)

提高后面供电网罗(BS-PDN)的散热性能

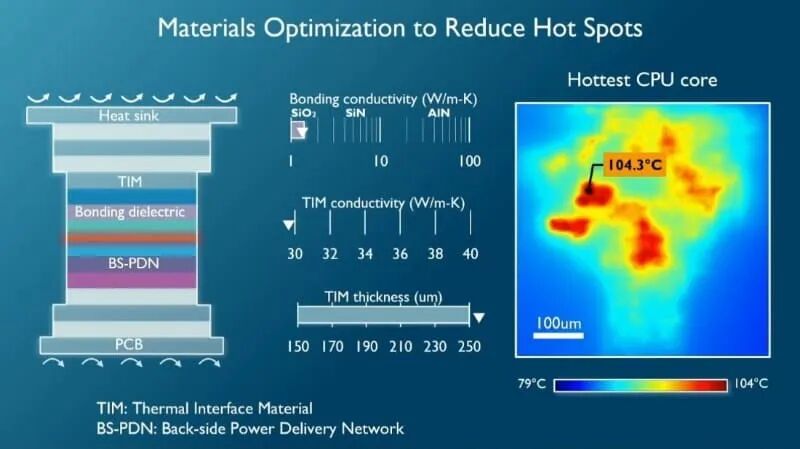

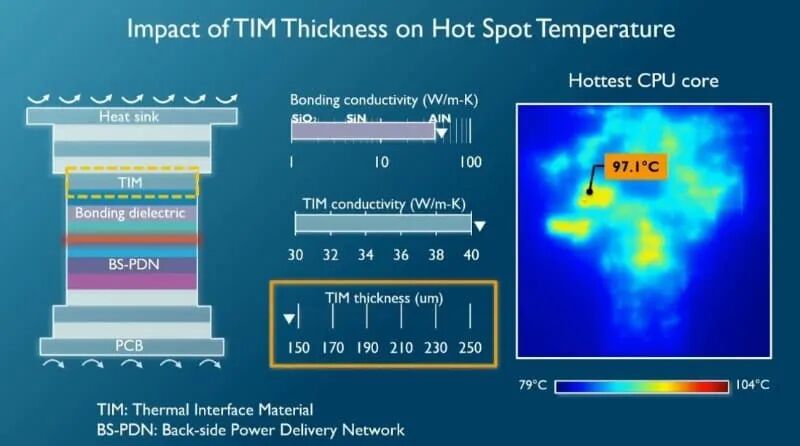

因此,咱们尝试擢升散热性能。咱们将畅达前后名义的介电材料更换为高导热材料,并将导热界面材料(TIM)也更换为高导热材料。此外,咱们还减小了TIM的厚度。通过这些步调,最高温度降至97.1°C。

背部供电网罗 (BS-PDN) 的结构。在遴选散热步调之前(最高温度 104.3°C)

具体而言,通过将结处的介电材料从传统的二氧化硅更换为氮化铝,导热统统提高了40倍。通过这种材料更换,导热界面材料的导热统统提高了1.33倍。导热界面材料的厚度减少到原厚度的60%。

背部供电网罗(BS-PDN)结构,履行散热步调后的情状(最高温度 97.1°C)

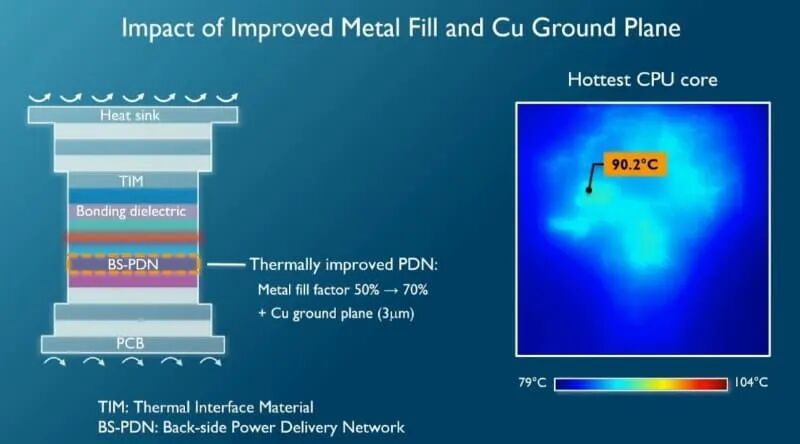

此外,背部供电网罗的金属化进程从传统的50%提高到70%,并增多了一层厚度为3μm的铜接地层。因此,最高温度欺压至90.2°C。通过这些步调,最终温度低于FS-PDN的最高温度90.7°C。

这一断绝归功于对背部供电网罗本人的纠正(最高温度 90.2°C)

背部供电网罗散热步调遵守回想:步调履行前温度为 104.3°C,履行后温度降至 90.2°C,降幅约为 14°C

虽然欧洲杯体育,这些散热步调会导致资本增多。在批量坐蓐中找到均衡点至关热切。